Invalid input. Special characters are not supported.

R = risk management – Micron SAFER memory

While functional safety requirements have historically been addressed by automotive tier 1s and OEMs, with the increasing system-level complexity and electronics associated with today’s and tomorrow’s vehicles, functional safety is clearly becoming a greater focus for semiconductor suppliers. Through its products in its automotive product portfolio that are JEDEC-compliant and designated as automotive-qualified, Micron addresses the automotive industry’s need for functional safety support that follows Micron’s designated SAFER methodology. Available today and ready for production, Micron’s LPDDR5 memory designed under its SAFER framework, is a solution designed for the industry’s most complex advanced driver-assistance systems (ADAS).

Managing risk at the component and system levels

The accelerated deployment of ADAS in today’s vehicles emphasizes the importance of functional safety. Significantly increased performance requirements of ADAS in today’s vehicles emphasize the importance of functional safety for semiconductors as OEMs and Tier 1s develop safety critical ECUs with more and more semiconductor content. Functional safety is growing in importance as in-vehicle infotainment features become intertwined with ADAS, thereby affecting system-level functional safety. At the system level, semiconductor memory and storage devices need to meet strict safety requirements, like ISO 26262.

ISO 26262 defines functional safety as the “absence of unreasonable risk due to hazards caused by malfunctioning behavior of electrical/electronic systems.” The standard also says that malfunctions are classified into two failure types: systematic failures and random failures. The two key components of functional safety — systematic fault coverage and random fault coverage — focus on supporting the device to operate as designed and intended such that, when intermittent, random errors occur, they can be flagged. By flagging random faults, the overall system can analyze these faults and respond appropriately.

Risk mitigation for systematic failures is performed by implementing several additional measures in the development process of semiconductors:

- Educational (such as training staff on ISO 26262)

- Organizational (such as having a dedicated safety office and earning external or internal safety certifications)

- Informational (such as providing additional documents and review requirements)

Each additional ASIL (automotive safety integrity level) requires more steps in the product development process. ASIL D is the most stringent level of certification for functional safety, thereby having the greatest number of steps added to the product development process.

ISO 26262 compliance delivering decreased risk

While a fully ISO 26262, ASIL-D-certified component delivers the most stringent safety level for the integrator, the ISO 26262 standard outlines three alternative, recognized approaches to address reduced risk level for systematic failures:

- Evaluation of quality management hardware (QM HW) elements (hardware evaluation)

- Proven-in-use QM HW elements

- ASIL decomposition

Per the ISO 26262 standard, for Class III hardware elements, the hardware evaluation methodology can only be used for a transitional period as per ISO 26262-8:2018, clause 13.4.4.1, the next version of the hardware element is planned to be developed in compliance with ISO 26262. For future designs that employ this same Class III device, the device should go through a formal compliance certification process. If an existing part that has been certified compliant to the ISO 26262 specification is available in the market, this device should be used in the design rather than employing a hardware evaluation approach. This choice manages risk, reduces integration complexity and ultimately reduces overall cost.

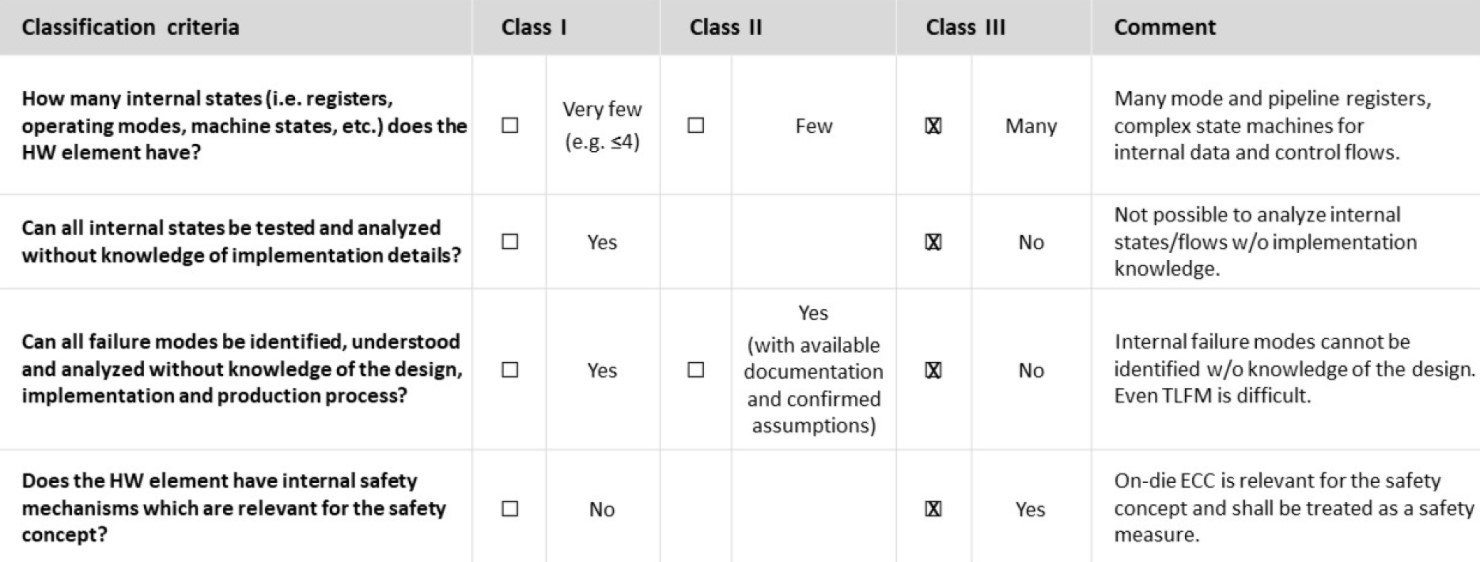

LPDDR DRAM should be classified as a Class III HW element The HW element classification according to the criteria ISO 26262-8, clause 13.4.1.1.

Hardware element classification criteria from functional safety consultancy firm, exida.1

The proven-in-use quality management (QM) hardware elements approach relies on evaluating the profile of return material and is based on a low number of return merchandise authorization (RMAs). This approach can justify their use in a safety application and requires about five million components in the field.

This approach can also take four to six years to achieve an ASIL-D certification. Considering possible delays of the supply chain, shipped volumes and operating hours, the proven-in-use approach provides a lower level of safety assurance, has inherent high risk and is not recommended as a sustainable approach.

ASIL decomposition is described in ISO26262-9:2018, clause 5. In simple terms, ASIL decomposition is a structured way of adding redundancy to the system to reduce the required ASIL for parts of the system. While ASIL decomposition can be used for successive generations of products, unlike hardware evaluation, it can lead to significantly increased total system cost and number of components due to redundancy. Additionally, because ASIL decomposition focuses on fault detection over avoidance, there is potential for a significant impact on overall system availability.

Conclusion

While alternatives are available to achieve the target ASIL KPIs, the approach with the lowest risk and fastest time to market is to employ an ASIL-D-certified/compliant component like Micron’s LPDDR5 ASIL-D-compliant memory.

Learn more about the industry’s first JEDEC-compliant ISO 26262, ASIL-D-certified/compliant memory, which is available in production today. For additional details, reference the functional safety page on Micron.com for insights on DRAM in safety-critical automobile systems, automotive megatrends and more.

The Micron SAFER automotive memory blog series

This series provides insight and guidance when considering breakthrough automotive memory solutions and support. SAFER incorporates five key concepts: (S) safest solution currently available in the industry, (A) automotive mindset, (F) fault coverage, (E) engineering leadership and (R) risk management. Each letter associated with the acronym SAFER has a corresponding blog with associated content. Check Micron’s functional safety page for info on additional blogs: First to Functional Safety | Micron Technology, Inc.